Cadence 推出全新RTL合成软体 Genus,强调透过采用多层次大规模平行架构,能使合成周转时间缩短高达五倍并可线性扩充至1千万实例(instance)以上大的设计。Cadence的合作夥伴Imagination Technologies采用Genus合成解决方案在其PowerVR GE7800 GPU,在不影响功耗、性能和面积目标,使合成周转时间加速高达五倍。

Cadence指出,随着SoC的设计规模与复杂度日益提升,一颗16奈米制程晶片上的实体模块(physical block)数量将超过500个,是40奈米制程的十倍之多。若要持续藉由扩增设计团队来为应付此设计规模成长,在实务上是不可行的。

而设计实现软体工具为什么无法跟上设计规模的成长主要原因在于,目前的合成、布局与最佳化工具无法有效地分散在多台机器上执行而不会影响功率、效能和面积(PPA)目标。同时,数位设计需要多次反覆的特质也是另一个因素,随着制程节点微缩,更复杂的实体设计规则使得模块层级(block-level)的合成设计必须大幅耗费合成runtime才能与后段的布局布线(P&R)更具关联性。

为了克服这些挑战,Cadence推出的新一代Genus合成工具便是专为缩小SoC“设计生产力落差”(design productivity gap)所设计。它具备优异的可扩充性,能平行处理大量的功能模块,可在多重核心与机器之间执行时序驱动型分散式合成作业,合成流程中所有主要步骤均能有效运用多部机器与各机器中的多重CPU核心。

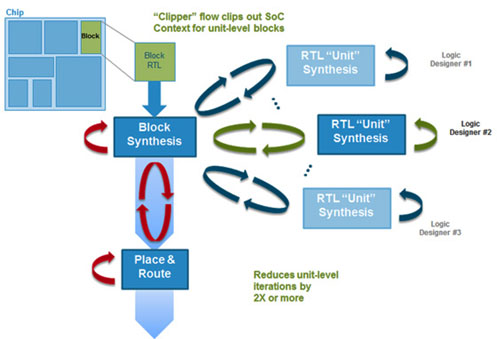

而透过最新的实体意识内容(physically aware context-generation)生成功能,设计中任何子集(subset)的完整时序与实体内容均可撷取,并于全面考量晶片层次时序与布局之下用于驱动RTL单元层次合成作业,藉此大幅减低晶片层次(chip-level)与单元层次(unit-level)合成周期的反覆率达2倍以上。

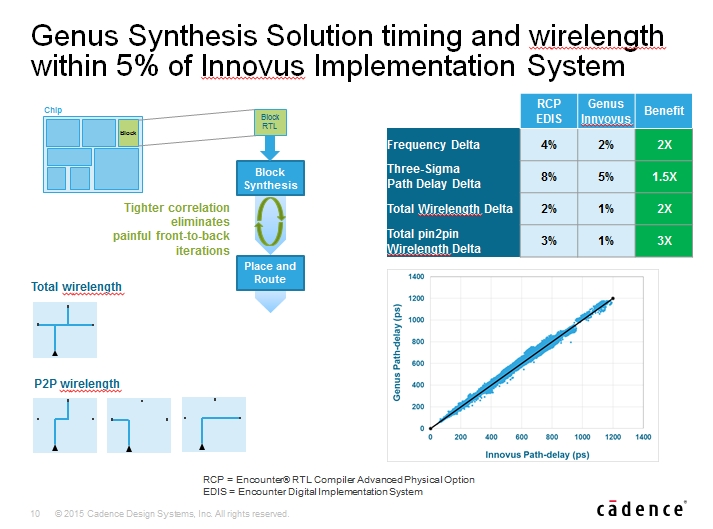

此外,Genus能与日前发布的Innovus设计实现软体工具紧密结合,共同将时序驱动型全域绕线器运行速度提升四倍,使合成至布局与绕线期间,时序与线长的关联性紧缩至5%以内。

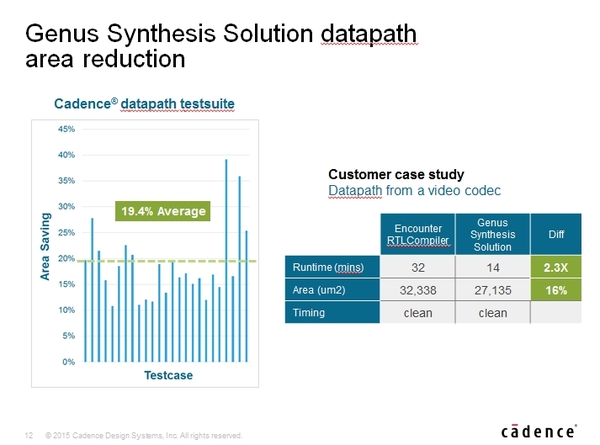

Genus合成方案还导入了新的全域解析演算法(Global analytical architecture-level),采用最新资料路径(datapath)最佳化引擎,可考量全盘设计中多种不同资料路径架构,再运用解析式解算器挑选可达成全域最佳化PPA的架构。此引擎不仅可降低资料路径面积达20%,更不会对性能造成任何影响。

Genus甫一推出便已获得合作夥伴Imagination Technologies的采用。Imagination是绘图处理器GPU IP的领先供应商,该公司表示,Genus合成解决方案可加速Imagination绘图核心及其他IP方案的设计收敛。在PowerVR GE7800 GPU上,相较之前解决方案,Genus合成解决方案可改善周转时间五倍,且不影响PPA。

Cadence Design Systems, Inc. unveiled the Cadence Genus Synthesis Solution, its next-generation register-transfer level (RTL) synthesis and physical synthesis engine, to address the productivity challenges faced by RTL designers.

Genus Synthesis Solution incorporates a multi-level massively parallel architecture that delivers up to 5X faster synthesis turnaround times and scales linearly beyond 10M instances. In addition, the tool’s new physically aware context-generation capability can reduce iterations between unit- and chip-level synthesis by 2X or more. This powerful combination enables up to 10X improvement in RTL design productivity.

Key Genus Synthesis Solution features and capabilities include:

– Massively parallel architecture – The tool performs timing-driven distributed synthesis of a design across multiple cores and machines. All key steps in the synthesis flow leverage both multiple machines and multiple CPU cores per machine.

– Physically aware context generation – The complete timing and physical context for any subset of a design can be extracted and used to drive RTL unit-level synthesis with full consideration of chip-level timing and placement, significantly reducing iterations between chip-level and unit-level synthesis runs.

– Unified global routing with Innovus Implementation System – Genus Synthesis Solution and Cadence Innovus Implementation System, a next-generation physical implementation solution, share an enhanced 4X faster timing-driven global router that enables tight correlation of both timing and wirelength to within 5 percent from synthesis to place and route.

– Global analytical architecture-level PPA optimization – The solution incorporates a new datapath optimization engine that concurrently considers many different datapath architectures across the whole design and then leverages an analytical solver to pick the architectures that achieve the globally optimal PPA. This engine delivers up to 20 percent reduction in datapath area without any impact on performance.

System Requirements: Linux

软件下载地址:

Download 百度云盘:

[erphpdown]https://pan.baidu.com/s/1pLRINph 密码:5sb1

解压密码: www.unyoo.com[/erphpdown]

联合优网

联合优网